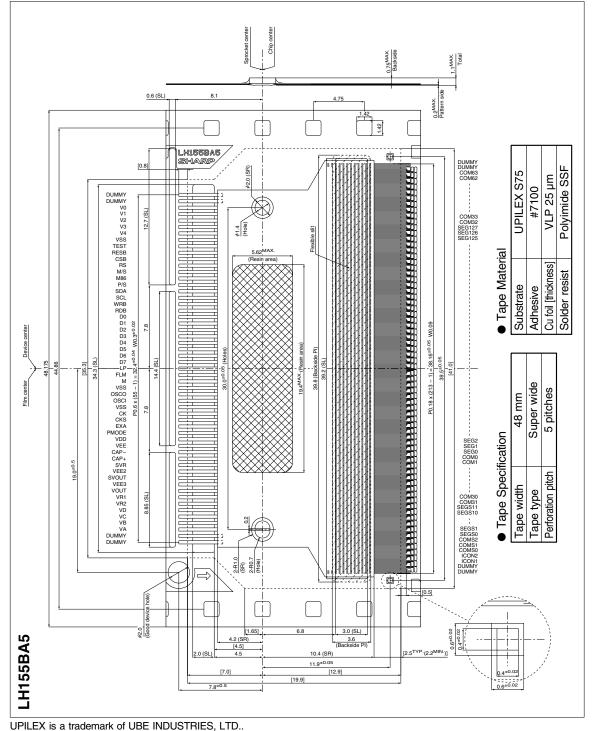

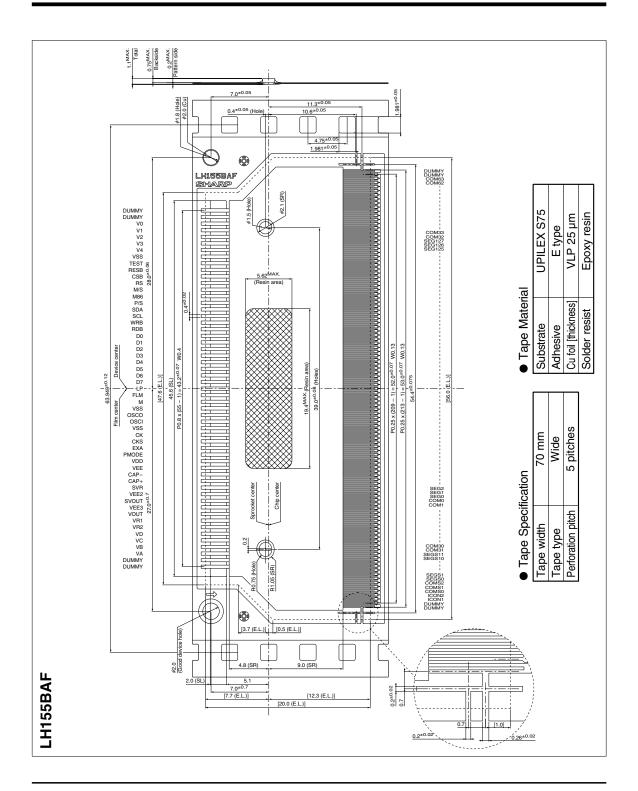

# LH155BA

# DESCRIPTION

The LH155BA is an LCD driver with a built-in RAM suitable for driving medium/small scale dot-matrix LCD panels, and which is capable of being directly connected to the bus line of a microcomputer. The LH155BA stores in the RAM the 8-bit parallel or serial displav data transferred from the microcomputer and generates LCD drive signals. Since the LH155BA features a bit-map type LCD driver that one bit of data in the display RAM corresponds to one dot in the LCD, there is a lot of freedom in displaying. The LH155BA has 128 segment outputs and 64 common outputs in a single chip, making it possible to create an LCD system with the fewest number of the chips. The LH155BA enables an LCD system for batteryoperated, hand-carrying information equipment by securing lower power consumption and wider operating voltage range.

# FEATURES

- Graphic display output pin : 64 x 128 pins

- Segment display output pin : 3 x 12 pins

- Icon display output pin : 1 x 1 pin

- LCD display by graphic display RAM

- Normal mode : RAM data "0"→not lighted, RAM data "1"→lighted

- Reverse mode: RAM data "1"→not lighted, RAM data "0"→lighted

- Display RAM memory capacity

- 128 x 64 = 8 192 bits (For graphic display)

- 12 x 3 = 36 bits (For segment display)

- $-1 \times 1 = 1$  bit (For icon display)

- General 8-bit MPU interface : Possible to directly connect 80-family and 68-family MPUs to bus line

- Possible to make serial interface

- Ratio of display duty cycle : 1/16, 1/32, 1/48 or 1/64 (selectable by command)

- 128-bit automatic transfer from display RAM to display data latch

# 128-Segment and 64-Common Outputs LCD Driver IC with A Built-in RAM

- Abundant command functions

- Display data read/write

- Setting up LCD alternating signal cycle

- Setting up display starting-line : per line

- Display ON/OFF

- Display control of normal and reverse modes

- Increment control of display RAM address

- Write control of read modifying

- Internal register read

- Power saving mode

- LCD drive power circuit

- Built-in booster circuit : Two, three or four times voltage boost is possible

- Built-in voltage converter : Generates LCD drive voltages (Vo, V1, V2, V3 and V4) based on the boosted voltage

- Built-in power bias ratio : 1/7 or 1/9 bias (selectable by command)

- Built-in electronic volume : Controllable in 16 steps

- Supply voltages

- Logic system : +1.8 to +5.5 V

- LCD drive system : +4.0 to +14.0 V

- Operating temperature : -30 to +85 °C

- Package : 260-pin TCP (Tape Carrier Package)

In the absence of confirmation by device specification sheets, SHARP takes no responsibility for any defects that may occur in equipment using any SHARP devices shown in catalogs, data books, etc. Contact SHARP in order to obtain the latest device specification sheets before using any SHARP device.

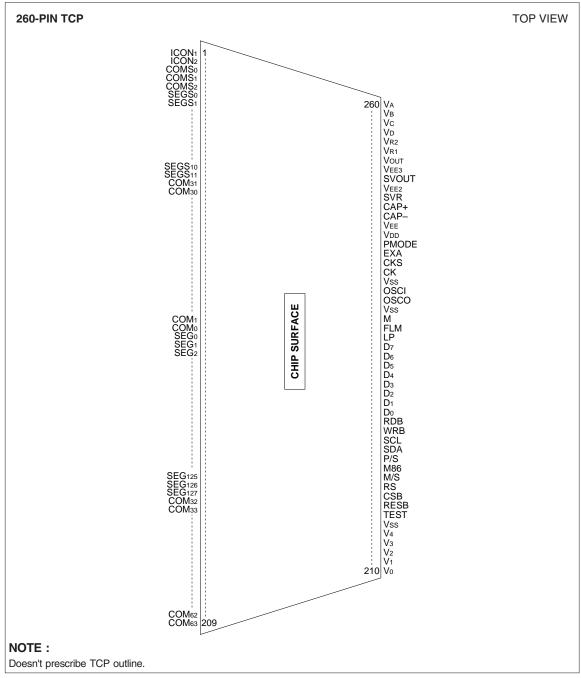

# **PIN CONNECTIONS**

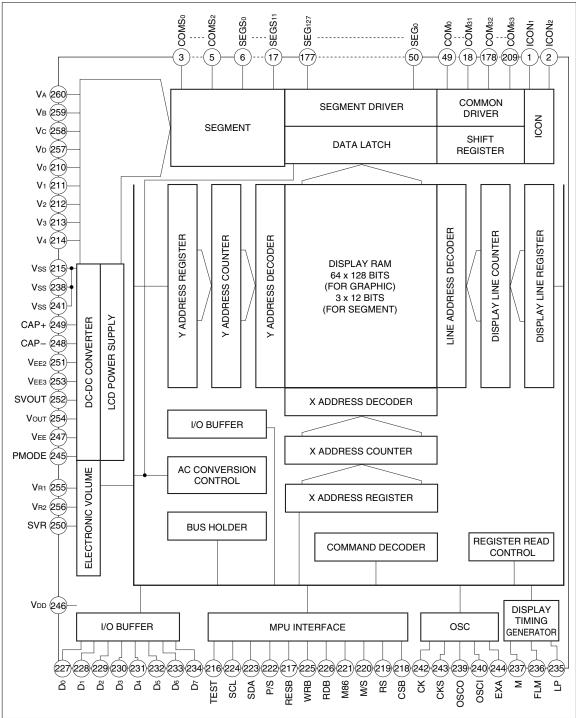

# **BLOCK DIAGRAM**

# **1. PIN DESCRIPTION**

# 1.1. Power Supply Pins

| SYMBOL                                                   | I/O                                                                                | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vdd                                                      | Power Supply                                                                       | Power supply pin for logic, connected to +1.8 to +5.5 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Vss                                                      | Power Supply                                                                       | Ground pin, connected to 0 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                          |                                                                                    | Bias power supply pins for LCD drive voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

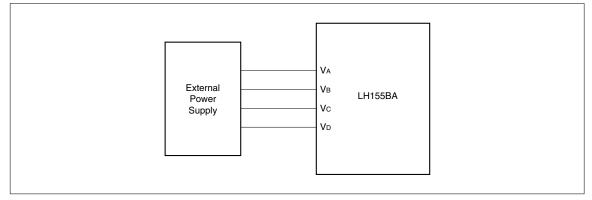

| V0<br>V1<br>V2<br>V3<br>V4<br>V4<br>VA<br>VB<br>VC<br>VD | Power Supply<br>Vo-V4 for<br>Graphic<br>Display<br>VA-VD for<br>Segment<br>Display | <ul> <li>When using an external power supply, convert impedance by using resistance-division of LCD drive power supply or operational amplifier before adding voltage to the pins.</li> <li>When using the external power supply, maintain the following power supply conditions.</li> <li>VSS &lt; V4 &lt; V3 &lt; V2 &lt; V1 &lt; V0, VSS ≤ VD &lt; VC &lt; VB &lt; VA</li> <li>When the power supply circuit is ON at master operation, LCD drive voltages of Vo to V4 are generated by the internal booster circuit and voltage converter. When using segment display, input VA, VB, VC and VD level externally.</li> <li>When using the internal power supply, be sure to connect each capacitor between V0 to V4, VA to VD, and VSS.</li> </ul> |

# 1.2. LCD Power Supply Circuit Pins

| SYMBOL | I/O           | DESCRIPTION                                                                          |  |  |  |  |  |  |

|--------|---------------|--------------------------------------------------------------------------------------|--|--|--|--|--|--|

| CAP+   | 0             | Connecting pin for the internal booster's capacitor + side.                          |  |  |  |  |  |  |

| CAF+   | 0             | The capacitor is connected between CAP- and CAP+.                                    |  |  |  |  |  |  |

| CAP-   | 0             | Connecting pin for the internal booster's capacitor - side.                          |  |  |  |  |  |  |

| CAP-   | 0             | The capacitor is connected between CAP+ and CAP                                      |  |  |  |  |  |  |

| VEE2   | 0             | Connecting pin for the internal booster's capacitor + side.                          |  |  |  |  |  |  |

| VEE2   | 0             | The capacitor is connected between Vss and VEE2.                                     |  |  |  |  |  |  |

| VEE3   | 0             | Connecting pin for the internal booster's capacitor + side.                          |  |  |  |  |  |  |

| VEE3   | 0             | The capacitor is connected between Vss and VEE3.                                     |  |  |  |  |  |  |

| VEE    | Power supply  | Voltage supply pin for generating boosted voltage in the internal booster circuit.   |  |  |  |  |  |  |

| VEE    | Power supply  | Usually the same voltage level as VDD.                                               |  |  |  |  |  |  |

| Vout   | Power supply/ | Output pin of boosted voltage in the internal booster circuit.                       |  |  |  |  |  |  |

| V001   | 0             | The capacitor must be connected between Vss and Vout.                                |  |  |  |  |  |  |

| SVOUT  | -             | Non-connected.                                                                       |  |  |  |  |  |  |

| VR1    | 1             | Used as input pins for graphic display voltage converter.                            |  |  |  |  |  |  |

| VR2    | I             | Voltage must be input between the VEE and VOUT pins by voltage divided by resistors. |  |  |  |  |  |  |

| SVR    | -             | Non-connected.                                                                       |  |  |  |  |  |  |

|        |               | Pin for controlling LCD power supply.                                                |  |  |  |  |  |  |

| PMODE  |               | A combination of PMODE pin and ON/OFF command of power supply (PON)                  |  |  |  |  |  |  |

|        |               | enables selection of a specific drive operation.                                     |  |  |  |  |  |  |

# 1.3. System Bus Pins

| SYMBOL | I/O | DESCRIPTION                                                                              |

|--------|-----|------------------------------------------------------------------------------------------|

| D7-D0  | I/O | 8-bit bi-directional data bus, connected to 8-bit MPU data bus.                          |

| CSB    | I   | Chip selection input pin that decoded address bus signal is input.                       |

|        |     | Distinguishes display RAM data/commands of D7 to D0 data transferred from MPU.           |

| RS     | I.  | 0 : The data of D7 to D0 show the display RAM data.                                      |

|        |     | 1 : The data of D7 to D0 show the command data.                                          |

|        |     | Initialized by setting to "L". The reset signals of the system are normally input. Reset |

| RESB   | I   | operation is performed in accordance with RESB signal level.                             |

|        |     | In connecting to 80-family MPU :                                                         |

|        |     | This RDB is a pin for connecting the RDB signal of 80-family MPU. When the               |

|        |     | signal enters in the "L" state, the data bus of this IC turns to the "output" state.     |

| RDB    | I   | In connecting to 68-family MPU :                                                         |

| (E)    |     | This RDB becomes a pin for connecting the enable clock signal of 68-family MPU.          |

|        |     | When the signal enters in the "H" state, the data bus of this IC turns to the "active"   |

|        |     | state.                                                                                   |

|        |     | In connecting to 80-family MPU :                                                         |

|        |     | This WRB is a pin for connecting the WRB signal of 80-family MPU, and when               |

|        |     | WRB signal is "L", this pin is "active".                                                 |

|        |     | The data bus signal is input at the rising edge of WRB signal.                           |

| WRB    | I.  | <ul> <li>In connecting to 68-family MPU :</li> </ul>                                     |

| (R/W)  |     | This WRB becomes a pin for connecting the R/W signal of controlling read/write of        |

|        |     | 68-family MPU.                                                                           |

|        |     | R/W = "H" : Read                                                                         |

|        |     | R/W = "L"∶Write                                                                          |

|        |     | MPU interface-type shift pin.                                                            |

|        |     | M86 = "H" : 68-family interface                                                          |

| M86    | I   | M86 = "L" : 80-family interface                                                          |

|        |     | Fixed to either "H" or "L".                                                              |

| SDA    | 1   | Serial-data input pin at time of serial interface selection.                             |

|        | -   | Serial clock pin at time of serial interface selection.                                  |

|        |     | Used to shift the SDA data by using the rising edge of SCL.                              |

| SCL    | I.  | Used to convert into 8-bit data by using the 8th clock at the rising edge of SCL in      |

|        |     | serial-to-parallel data processing.                                                      |

|        |     | After data-transferring, or when making no access, be sure to set to "L".                |

|        |     | Used to shift between parallel interface and serial interface.                           |

|        |     | P/S Chip selection Data identification Data Read/Write Serial clock                      |

|        |     | H CSB RS D7-D0 RDB, WRB –                                                                |

| P/S    | 1   | L CSB RS SDA Write only SCL                                                              |

|        | •   | P/S = "H" for parallel input. Fix SDA and SCL pins to either "H" or "L".                 |

|        |     | P/S = "L" for serial input. Fix D7 to D0 pins to High-Z, RDB and WRB pins to either      |

|        |     | "H" or "L".                                                                              |

| TEST   |     | For testing. Fix to "L".                                                                 |

|        | 1   |                                                                                          |

# 1.4. LCD Drive Circuit Signals

| SYMBOL      | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |

|-------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

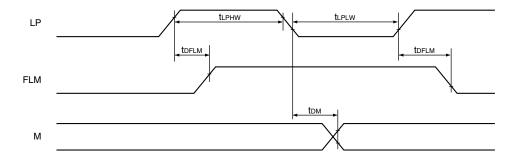

| LP          | I/O | The latching signal of display data to count up the display line counter at the rising, and to output the LCD drive signals at the falling.<br>M/S = "H" : Output for master mode                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |

|             |     | M/S = "L" : Input for slave mode                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |

|             |     | I/O pin for LCD synchronous signals (first line marker).                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |  |

|             |     | When FLM pin is set to "H", the display starting line address is preset in the display                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

| FLM         | I/O | line counter.                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |  |

|             |     | M/S = "H" : Output for master mode                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |  |

|             |     | M/S = "L" : Input for slave mode                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |

|             |     | I/O pin for alternating signals of LCD drive output.                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |

| м           | I/O | M/S = "H" : Output for master mode                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |  |

|             |     | M/S = "L" : Input for slave mode                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |

|             |     | Used to select either master or slave mode operation.                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

|             |     | M/S State OSC P.S.circuit LP FLM M                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |  |

| M/S         | I   | H Master Enabled Enabled Output Output Output                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |  |

|             |     | L Slave Disabled Disabled Input Input Input                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |

|             |     | Fix to "H" or "L" at this pin.                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |

| SEG0-SEG127 | Ο   | Segment output pins for graphic display.<br>According to the data of the display RAM data,<br>non-lighted at "0", lighted at "1" (Normal mode)<br>non-lighted at "1", lighted at "0" (Reverse mode)<br>and, by a combination of M signal and display data, one signal level among Vo, V2,<br>V3, and Vss is selected.<br>M Signal<br>Display RAM Data<br>Normal Mode<br>V2<br>V0<br>V3<br>V3<br>V3<br>Vss |  |  |  |  |  |  |  |  |  |

| COM0-COM63  | Ο   | Reverse Mode     V0     V2     Vss     V3       Common output pins for graphic display.       By a combination of the scanning data and M signals, one signal level among V0, V1,       V4 and Vss is selected.       Data     M     Output level       H     H     Vss       L     H     V1       H     L     V0       L     L     V4                                                                    |  |  |  |  |  |  |  |  |  |

| SYMBOL       | I/O |                                                                    | DESCRI               | PTION                  |                   |  |  |  |  |  |  |

|--------------|-----|--------------------------------------------------------------------|----------------------|------------------------|-------------------|--|--|--|--|--|--|

|              |     | Common output pins for segment display.                            |                      |                        |                   |  |  |  |  |  |  |

|              | 0   | When executing SEGON command, it functions as common output pin.   |                      |                        |                   |  |  |  |  |  |  |

| COMS0-COMS2  | 0   |                                                                    | SEG ON               | SEG OFF                |                   |  |  |  |  |  |  |

|              |     | COMS state                                                         | Display              | Vss                    |                   |  |  |  |  |  |  |

|              |     | Segment output pins for                                            | or segment display.  |                        |                   |  |  |  |  |  |  |

|              |     | When executing SEGON command, it functions as segment output pins. |                      |                        |                   |  |  |  |  |  |  |

| SEGS0-SEGS11 | 0   |                                                                    | SEGON = "1"          | SEGON = "0"            |                   |  |  |  |  |  |  |

|              |     | SEGS state                                                         | Display              | Vss                    |                   |  |  |  |  |  |  |

|              |     | Common output pin for icon display.                                |                      |                        |                   |  |  |  |  |  |  |

|              |     | When executing ICON                                                | command, it function | s as common icon di    | splay output pin. |  |  |  |  |  |  |

| ICON1        | 0   |                                                                    | ICON = "1"           | ICON = "0"             |                   |  |  |  |  |  |  |

|              |     | ICON1 state                                                        | Display              | Vss                    |                   |  |  |  |  |  |  |

|              |     | Data output pin for ico                                            | n display.           |                        |                   |  |  |  |  |  |  |

|              |     | When executing ICON                                                | command, it function | s as data icon display | y output pin.     |  |  |  |  |  |  |

| ICON2        | 0   |                                                                    | ICON = "1"           | ICON = "0"             |                   |  |  |  |  |  |  |

|              |     | ICON2 state                                                        | Display              | Vss                    |                   |  |  |  |  |  |  |

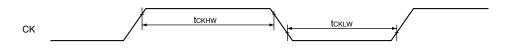

# 1.5. Pins for Oscillation Circuit

| SYMBOL | I/O | DESCRIPTION                                                                            |

|--------|-----|----------------------------------------------------------------------------------------|

| OSCI   | I   | Foodbook registered connecting ain for the internal agaillation airquit                |

| OSCO   | 0   | Feedback-resistance connecting pin for the internal oscillation circuit.               |

| EXA    | I   | Input pin of icon clock.                                                               |

|        |     | Input pin of display master clock at master mode.                                      |

| СК     | I   | When using CK pin as an input of the master clock, fix OSCI pin to Vss.                |

|        |     | When using the internal oscillation circuit as the display master clock, fix CK pin to |

|        |     | Vss.                                                                                   |

|        |     | Selection input pin of display master clock at master mode.                            |

| CKS    | I   | CKS = "H" : Input the external clock to CK pin.                                        |

|        |     | CKS = "L" : The internal oscillation circuit by using OSCI and OSCO pins is used.      |

\* Master clock : Clock for oscillation circuit or external clock.

# 1.6. Input/Output Circuits

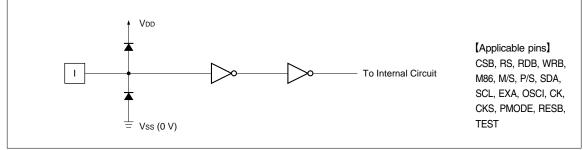

Fig. 1 Input Circuit

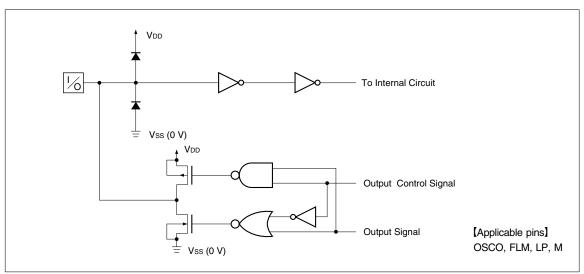

Fig. 2 Input/Output Circuit (1)

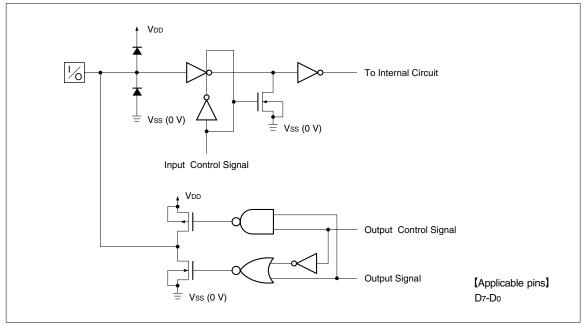

Fig. 3. Input/Output Circuit (2)

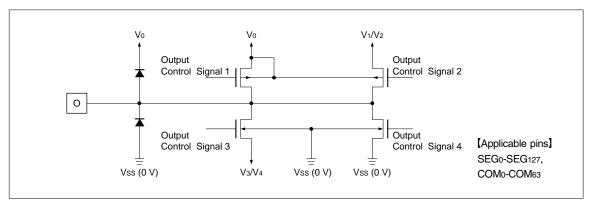

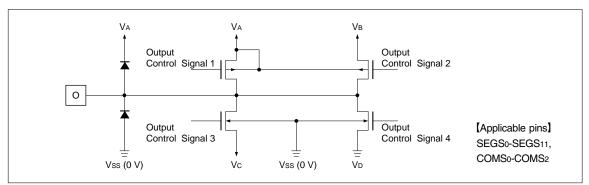

Fig. 4. LCD Drive Output Circuit (Graphic Display)

Fig. 5. LCD Drive Output Circuit (Segment Display)

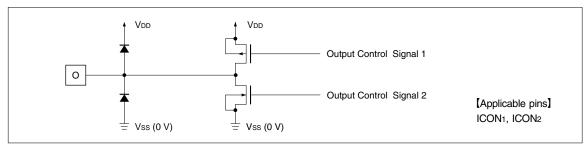

Fig. 6. LCD Drive Output Circuit (Icon Display)

# 2. FUNCTIONAL DESCRIPTION

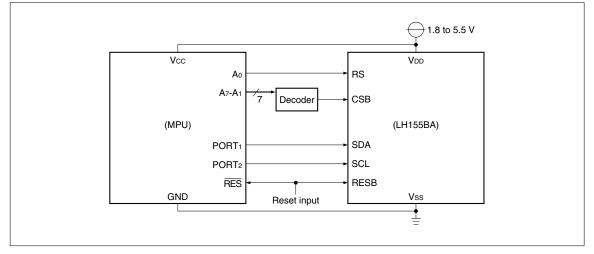

#### 2.1. MPU Interface

#### 2.1.1. INTERFACE TYPE SELECTION

The LH155BA transfers data through 8-bit parallel I/O (D7 to D0) or serial data input (SDA, SCL). The selection between parallel interface and serial interface is made by setting the state of P/S pin to "H" or "L".

When selecting serial interface, data-reading cannot be performed, but data-writing can.

| P/S | I/F TYPE | CSB | RS | RDB | WRB | M86 | SDA | SCL | DATA     |

|-----|----------|-----|----|-----|-----|-----|-----|-----|----------|

| Н   | Parallel | CSB | RS | RDB | WRB | M86 | -   | -   | D7 to D0 |

| L   | Serial   | CSB | RS | -   | -   | -   | SDA | SCL | -        |

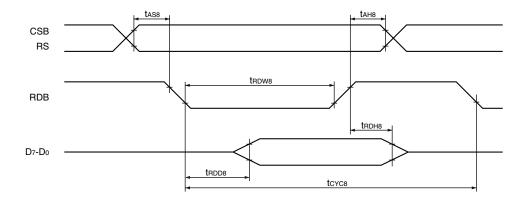

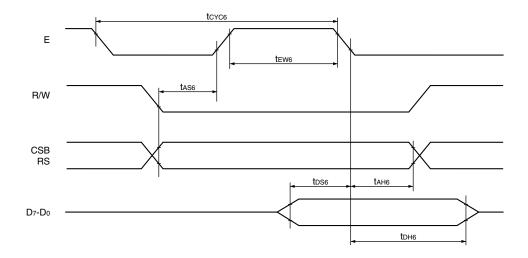

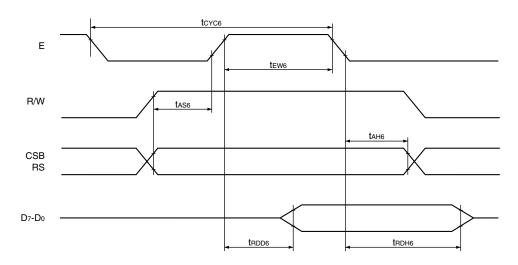

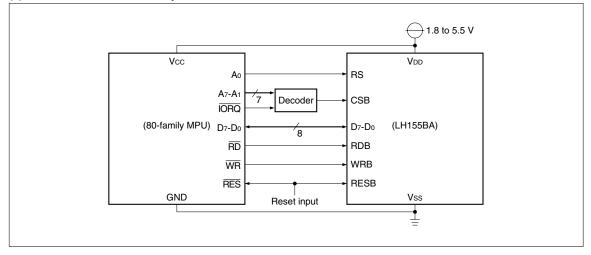

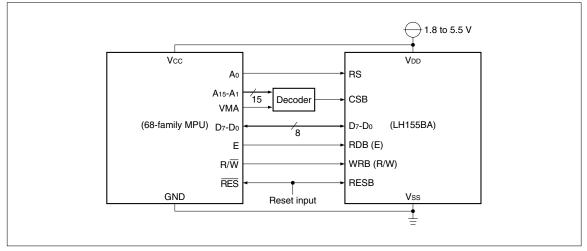

#### 2.1.2. PARALLEL INPUT

The LH155BA can transfer data in parallel by directly connecting 8-bit MPU to the data bus when parallel interface is selected with P/S pin.

As an 8-bit MPU, either 80-family MPU interface or 68-family MPU interface is selected with M86 pin.

| M86 | MPU TYPE      | CSB | RS | RDB | WRB | DATA     |

|-----|---------------|-----|----|-----|-----|----------|

| Н   | 68-family MPU | CSB | RS | E   | R/W | D7 to D0 |

| L   | 80-family MPU | CSB | RS | RDB | WRB | D7 to D0 |

#### 2.1.3. DATA IDENTIFICATION

The LH155BA can identify the data of 8-bit data bus by combinations of RS, RDB and WRB signals.

| RS | 68-FAMILY | 80-FA | AMILY | FUNCTION                     |

|----|-----------|-------|-------|------------------------------|

| нэ | R/W       | RDB   | WRB   | FUNCTION                     |

| 1  | 1         | 0     | 1     | Reads from internal register |

| 1  | 0         | 1     | 0     | Writes to internal register  |

| 0  | 1         | 0     | 1     | Reads from display data RAM  |

| 0  | 0         | 1     | 0     | Writes to display data RAM   |

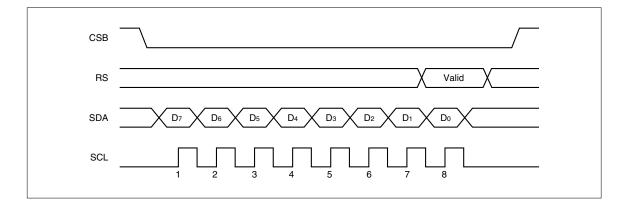

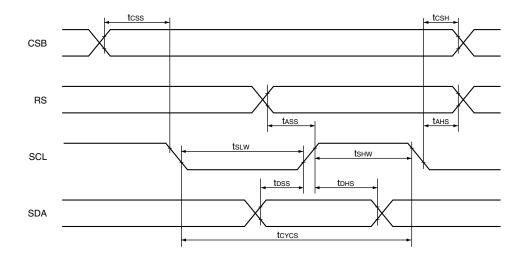

#### 2.1.4. SERIAL INTERFACE

The serial interface of LH155BA can accept inputs of SDA and SCL in the chip selection state (CSB = "L"). When not in the chip selection state, the internal shift register and counter are reset to their initial condition.

Serial data SDA are input sequentially in order of D7 to D0 at the rising edge of serial clock (SCL) and are converted into 8-bit parallel data (by serial to parallel conversion) at the rising edge of the 8th serial clock, being processed in accordance with the data. The identification whether the serial data inputs (SDA) are display data or commands is judged by input to RS pin.

RS = "L" : Display data

RS = "H" : Commands

After completing 8-bit data transferring, or when making no access, be sure to set serial clock input (SCL) to "L".

Protection of SDA and SCL signals against external noise should be taken in actual wiring. To prevent the successive recognition errors of transferring data from external noise, release the chip selection state (CSB = "H") at every completion of 8-bit data transferring.

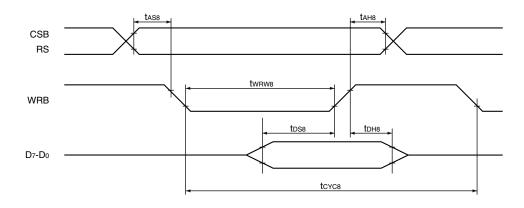

#### 2.2. Access to Display RAM and Internal Register

The LH155BA makes access to display RAM, and internal register by data bus D7 to D0, chip selection CSB pin, display RAM/register shifting RS pin, and read/write control RDB and WRB pins. When CSB is at "H", it is in non-selective state and cannot access display RAM and internal registers. When making access to them, set CSB to "L".

The access to either display RAM or internal registers can be shifted by RS input.

RS = "L" : Display RAM data

RS = "H" : Internal command register

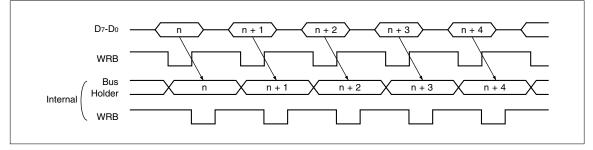

The data of 8-bit data bus D7 to D0 are written by write-operation after address setting through MPU. The timing of write is at the rising of WRB for 80-family MPU and at the falling of E for 68-family

MPU respectively.

Write is internally processed by intermediately placing the bus holder in the internal data bus. During data writing from MPU, the data are temporally held in the bus holder, then they are written by the time of the next cycle.

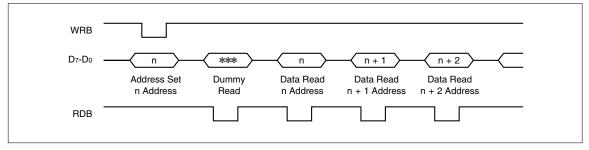

Since the read sequence of display RAM data is limited, note that when address set is made, the designated address data are not output to read command immediately after the address set, but are output when the second data are read, resulting in requiring one time dummy read.

Dummy read is always required one time after address set and write cycle.

Data Read Operation

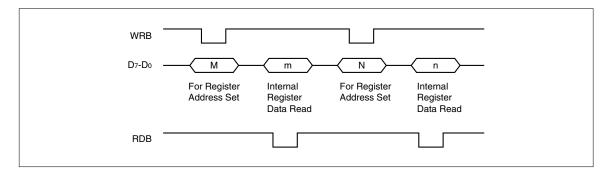

# 2.3. Read of Internal Register

The LH155BA reads not only display RAM, but also the internal registers. Read addresses (0H, 2H-EH) are allotted to each internal register. In reading the

internal registers, the addresses of internal registers allotted to read are written in the registers for internal register read and then are read.

# 2.4. Display Mode

The LH155BA has 3 display modes.

One is for graphic display mode and one is for segment display mode and the other is for icon display mode. Since 3 modes can be used independently by command, the suitable display mode can be selected to drive the device with minimum circuit for lower supply current operation.

#### 2.4.1. GRAPHIC DISPLAY MODE

This mode is built in 64 x 128 bits SRAM and 64common x 128-segment output.

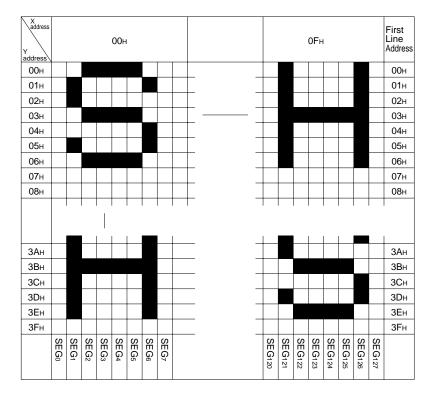

Graphic display's memory map is shown below.

When standby mode and sleep mode, power supply circuit is stopped and output pin is specified Vss level.

The memory for graphic display is accessed by 8 bits at one time.

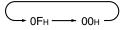

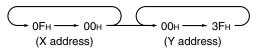

X address is from 00H to 0FH and Y address is from 00H to 3FH.

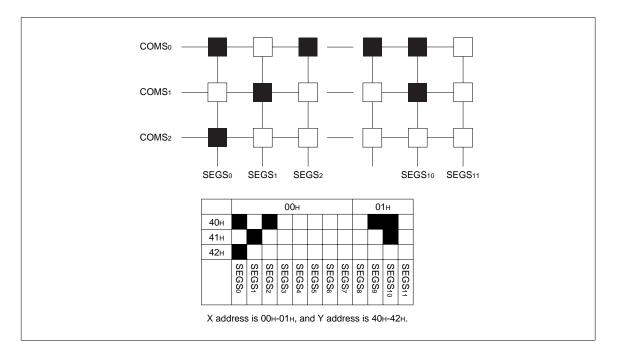

#### 2.4.2. SEGMENT DISPLAY MODE

This mode enables 3 x 12 bits memory and 3 COMS x 12 SEGS output.

Segment display's memory map is below.

Bias is fixed to 1/3. When display OFF, each output pin is specified Vss level.

X address is from 00H to 01H, and Y address is from 40H to 42H.

Segment display mode and graphic display mode are independent of each other.

When using segment display mode, lower power operation is possible.

When using slave mode, input clock for segment display at EXA pin (500 Hz : Duty 50%), and this time, EXA flag (EH register : See Section 4.14. "Power Control (3) Register Set") must be fixed to "H".

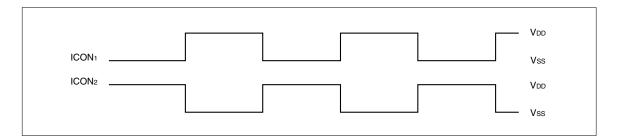

#### 2.4.3. ICON DISPLAY MODE

This mode enables 2 output pins for icon display and this mode can display 1 icon.

Source are VDD and Vss. Since this mode is independent of other mode completely, when using this mode, lower power operation is possible. Waveform of this mode is below. To display, use internal clock or external clock.

When using external clock, input clock pulse to EXA pin (120 Hz : Duty 50%).

When using icon display and segment display, input 500 Hz, duty 50% pulse.

# 2.5. Display Starting Line Register

This register is for determining display starting line (usually the most upper line) corresponding to COMo when displaying the display data RAM.

The register is also used in picture-scrolling.

The 6-bit display starting address is set in this register by display starting line setting command.

The register is preset every timing of FLM signal variation in the display line counter. The line counter counts up being synchronized with LP input and generates line addresses which sequentially read out 128-bit data from display RAM to LCD drive circuit.

# 2.6. Addressing of Display RAM

Display RAM consists of 128 x 64 bits memory, and enables access in 8-bit unit to an address specified by X address and Y address from MPU.

It is possible to set up the addresses X and Y so that they can increment automatically with the address control register. The increment is made every time display RAM is read or written from MPU. (See **Section 4. "COMMAND FUNCTION"**.) Though the X direction side is selected by X address while the Y direction side by Y address, 10H-FFH in the X address are inhibited and do not have the X address set in these addresses.

In the Y direction side, the 128-bit display data are internally read into the display data latch circuit at the rising of LP every one line cycle, and are output from the display data latch circuit at the falling of LP. 43H-FFH in the Y address are inhibited and do not have the Y address set in these addresses.

When FLM signals being output in one frame cycle are at "H", the value in the display starting line register are preset in the line counter and the line counter counts up at the falling of LP signals.

The display line address counter is synchronized with each timing signal of the LCD system to operate and is independent of address counters X and Y.

# 2.7. Display RAM Data and LCD

One bit of display RAM data corresponds to one dot of LCD. Normal display and reverse display by REV register are set up as follows.

- Normal display (REV = 0) : RAM data = "0"; not lighted RAM data = "1"; lighted

- Reverse display (REV = 1) : RAM data = "0"; lighted RAM data = "1"; not lighted

# 2.8. Segment Display Output Order/ Reverse Set Up

The order of display outputs, SEG0 to SEG127 can be reversed by reversing access to display RAM from MPU by using REF register, to lessen the limitation on placing IC when composing an LCD module.

# 2.9. Relationship between Display RAM and Address

(Configuration of display starting line address "00H")

| ₽ 1               |                  |       |                  | X =              | 0FH  | ł              |                |                |                  |                  |                   | X =                   | 0E⊦               | ł                 |                   |                   |                        |                    |                    | X =                | 00н                | I                  |                    |         |     | st _                 |

|-------------------|------------------|-------|------------------|------------------|------|----------------|----------------|----------------|------------------|------------------|-------------------|-----------------------|-------------------|-------------------|-------------------|-------------------|------------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|---------|-----|----------------------|

| 1   0<br>REF      |                  |       |                  | X =              | 00н  | ł              |                |                |                  |                  |                   | X =                   | 01⊦               | ł                 |                   |                   |                        |                    | 2                  | X =                | 0FH                |                    |                    |         |     | Lanting Comm         |

| 1 0<br>SWAP       | D7               | $D_6$ | $D_{5}$          | ₽4               | Δ    | D <sub>2</sub> | Ā              | Ď              | D'               | $D_6$            | $D_{5}$           | <b>D</b> <sub>4</sub> | Da                | D₂                | Ā                 | Ď                 | <br>₽,                 | $D_6$              | $D_5$              | <b>D</b><br>4      | Ω                  | $D_2$              | Ā                  | Ď       | G   | Comn<br>Display      |

| AP 0              | Ď                | Ā     | $D_2$            | ß                | D4   | D2             | D <sup>6</sup> | D <sup>2</sup> | Ď                | Ā                | $D_{2}$           | D₃                    | $D_4$             | $D_{5}$           | D <sup>6</sup>    | D2                | <br>Ô                  | Ā                  | $D_2$              | Ω                  | D4                 | D25                | D°                 | D'      |     |                      |

| 00н               |                  |       |                  |                  |      |                |                |                |                  |                  |                   |                       |                   |                   |                   |                   |                        |                    |                    |                    |                    |                    |                    |         | 00н | COM0                 |

| <b>01</b> н       |                  |       |                  |                  |      |                |                |                |                  |                  |                   |                       |                   |                   |                   |                   |                        |                    |                    |                    |                    |                    |                    |         | 01н | COM1                 |

| 02н               |                  |       |                  |                  |      |                |                |                |                  |                  |                   |                       |                   |                   |                   |                   |                        |                    |                    |                    |                    |                    |                    |         | 02н | En COM2              |

| 03н               |                  |       |                  |                  |      |                |                |                |                  |                  |                   |                       |                   |                   |                   |                   |                        |                    |                    |                    |                    |                    |                    |         | 03н | a COM3               |

| 04н               |                  |       |                  |                  |      |                |                |                |                  |                  |                   |                       |                   |                   |                   |                   |                        |                    |                    |                    |                    |                    |                    |         | 04н | ad COM3<br>ress COM4 |

| 05н               |                  |       |                  |                  |      |                |                |                |                  |                  |                   |                       |                   |                   |                   |                   |                        |                    |                    |                    |                    |                    |                    |         | 05н | <sup>66</sup> СОМ5   |

| 06н               |                  |       |                  |                  |      |                |                |                |                  |                  |                   |                       |                   |                   |                   |                   |                        |                    |                    |                    |                    |                    |                    |         | 06н | COM6                 |

| 07н               |                  |       |                  |                  |      |                |                |                |                  |                  |                   |                       |                   |                   |                   |                   |                        |                    |                    |                    |                    |                    |                    |         | 07н | COM7                 |

| 08н               |                  |       |                  |                  |      |                |                |                |                  |                  |                   |                       |                   |                   |                   |                   |                        |                    |                    |                    |                    |                    |                    |         | 08н | COM8                 |

| 09н               |                  |       |                  |                  |      |                |                |                |                  |                  |                   |                       |                   |                   |                   |                   |                        |                    |                    |                    |                    |                    |                    |         | 09н | COM9                 |

| 0Ан               |                  |       |                  |                  |      |                |                |                |                  |                  |                   |                       |                   |                   |                   |                   |                        |                    |                    |                    |                    |                    |                    |         | 0Ан | COM10                |

| 0Вн               |                  |       |                  |                  |      |                |                |                |                  |                  |                   |                       |                   |                   |                   |                   |                        |                    |                    |                    |                    |                    |                    |         | 0Вн | COM11                |

| 0Сн               |                  |       |                  |                  |      |                |                |                |                  |                  |                   |                       |                   |                   |                   |                   |                        |                    |                    |                    |                    |                    |                    |         | 0Сн | COM12                |

| 0Dн               |                  |       |                  |                  |      |                |                |                |                  |                  |                   |                       |                   |                   |                   |                   |                        |                    |                    |                    |                    |                    |                    |         | 0Dн | COM13                |

| 0Ен               |                  |       |                  |                  |      |                |                |                |                  |                  |                   |                       |                   |                   |                   |                   |                        |                    |                    |                    |                    |                    |                    |         | 0Ен | COM14                |

| 0 <b>F</b> н      |                  |       |                  |                  |      |                |                |                |                  |                  |                   |                       |                   |                   |                   |                   |                        |                    |                    |                    |                    |                    |                    |         | 0FH | COM15                |

|                   |                  |       |                  |                  |      |                |                |                |                  |                  |                   |                       |                   |                   |                   |                   |                        |                    |                    |                    |                    |                    |                    |         |     |                      |

| 37н               |                  |       |                  |                  |      |                |                |                |                  |                  |                   |                       |                   |                   |                   |                   |                        |                    |                    |                    |                    |                    |                    |         | 37н | COM55                |

| 38н               |                  |       |                  |                  |      |                |                |                |                  |                  |                   |                       |                   |                   |                   |                   |                        |                    |                    |                    |                    |                    |                    |         | 38н | COM56                |

| 39н               |                  |       |                  |                  |      |                |                |                |                  |                  |                   |                       |                   |                   |                   |                   |                        |                    |                    |                    |                    |                    |                    |         | 39н | COM57                |

| ЗАн               |                  |       |                  |                  |      |                |                |                |                  |                  |                   |                       |                   |                   |                   |                   |                        |                    |                    |                    |                    |                    |                    |         | ЗАн | COM58                |

| 3Вн               |                  |       |                  |                  |      |                |                |                |                  |                  |                   |                       |                   |                   |                   |                   |                        |                    |                    |                    |                    |                    |                    |         | ЗВн | COM59                |

| 3Сн               |                  |       |                  |                  |      |                |                |                |                  |                  |                   |                       |                   |                   |                   |                   |                        |                    |                    |                    |                    |                    |                    |         | 3Сн | COM60                |

| 3Dн               |                  |       |                  |                  |      |                |                |                |                  |                  |                   |                       |                   |                   |                   |                   |                        |                    |                    |                    |                    |                    |                    |         | 3Dн | COM61                |

| 3Ен               |                  |       |                  |                  |      |                |                |                |                  |                  |                   |                       |                   |                   |                   |                   |                        |                    |                    |                    |                    |                    |                    |         | 3Ен | COM62                |

| 3Fн               |                  |       |                  |                  |      |                |                |                |                  |                  |                   |                       |                   |                   |                   |                   |                        |                    |                    |                    |                    |                    |                    |         | ЗFн | COM63                |

| Segment<br>Output | SEG <sub>0</sub> | SEG1  | SEG <sub>2</sub> | SEG <sub>3</sub> | SEG4 | SEG5           | SEG6           | SEG7           | SEG <sub>8</sub> | SEG <sub>9</sub> | SEG <sub>10</sub> | SEG11                 | SEG <sub>12</sub> | SEG <sub>13</sub> | SEG <sub>14</sub> | SEG <sub>15</sub> | <br>SEG <sub>120</sub> | SEG <sub>121</sub> | SEG <sub>122</sub> | SEG <sub>123</sub> | SEG <sub>124</sub> | SEG <sub>125</sub> | SEG <sub>126</sub> | SEG 127 |     | $\$                  |

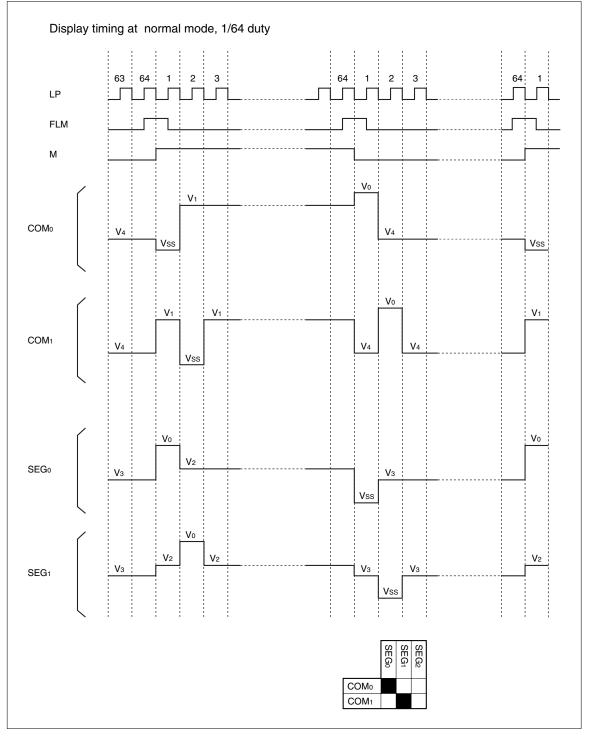

# 2.10. Display Timing Generator

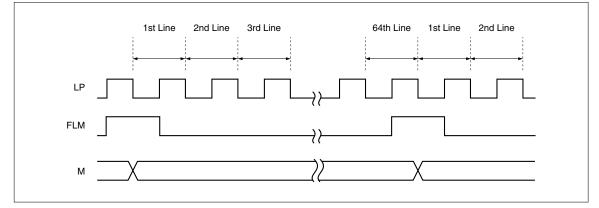

The display timing generator generates a timing clock necessary for internal operation and timing pulses (LP, FLM, and M) by inputting the master clock CK or by the oscillation circuit of OSCI and OSCO.

By setting up master/slave mode (M/S), the state of timing pulse pins and the timing generator changes.

| M/S | MODE   | LP     | М      | FLM    | STATE OF TIMING    |  |  |  |

|-----|--------|--------|--------|--------|--------------------|--|--|--|

| PIN | MODE   | PIN    | PIN    | PIN    | GENERATOR          |  |  |  |

|     | Slove  | Input  | Input  | Input  | Stop of LP, M, FLM |  |  |  |

|     | Slave  | input  | input  | input  | generation circuit |  |  |  |

| Н   | Master | Output | Output | Output | Operating state    |  |  |  |

**Display Timing Pulse Pins and Timing Generator State**

# 2.11. Signal Generation to Display Line Counter, and Display Data Latching Circuit

Both the clock to the line counter and latching signals to display data latching circuit from the display clock (LP) are generated.

Synchronized with the display clock, the line addresses of display RAM are generated and 128bit display data are latched to display-data latching circuit to output to the LCD drive circuit (SEG output).

Readout of the display data to the LCD drive circuit is completely independent of MPU. Therefore, a MPU that has no relationship the readout operation of the display data can access it.

# 2.12. Generation of The Alternating Signal (M) and The Synchronous Signal (FLM)

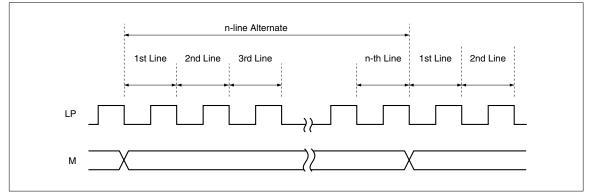

LCD alternating signal (M) and synchronous signal (FLM) are generated by the display clock (LP). The FLM generates alternated drive waveform to the LCD drive circuit. Normally, the FLM generates alternated drive waveform every frame unit (M-signal level is reversed every one frame).

But by setting up data (n - 1) in an n-line reverse register and n-line alternating command (NLIN) at "H", n-line reverse waveform is generated.

When the LH155BA is used in multi-chip, the signals of LP, FLM, and M must be sent from master side in the slave operation.

# 2.13. Display Data Latching Circuit

Display data latching circuit temporally latches display data that is output display data to LCD drive circuit from display RAM every one common period. Normal display/reverse display, display ON/OFF, and display all ON commands are operated by controlling data in the latch. And no data within display RAM changes.

# 2.14. Output Timing of LCD Driver

# 2.15. LCD Drive Circuit

This drive circuit generates 4 levels of LCD drive voltage. The circuit has 128 segment outputs and 64 common outputs and outputs combined display data and M signal. A common drive circuit that has a shift register sequentially outputs common scan signals.

# 2.16. Oscillation Circuit

The frequency of this CR oscillator is controlled by the feedback resistor RF.

The output from this oscillator is used as the timing signal source of the display and the boosting clock to the booster circuit. This is valid only in the master operation mode.

During the slave operation mode, maintain OSCI pin at Vss and OSCO pin open (NC).

When in the master operation mode and if external clock is used, maintain OSCI pin at Vss and OSCO pin open (NC), and feed the clock to CK pin. The duty cycle of the external clock must be 50%.

The CKS pin selects either internal oscillation circuit or external clock.

|     | MASTE    | R MODE     | SLAVE MODE |            |  |  |  |  |

|-----|----------|------------|------------|------------|--|--|--|--|

| CKS | OSC      | External   | OSC        | External   |  |  |  |  |

|     | 030      | Clock (CK) | 030        | Clock (CK) |  |  |  |  |

| L   | Enabled  | Disabled   | Disabled   | Disabled   |  |  |  |  |

| Н   | Disabled | Enabled    | Disabled   | Disabled   |  |  |  |  |

# 2.17. Power Supply Circuit

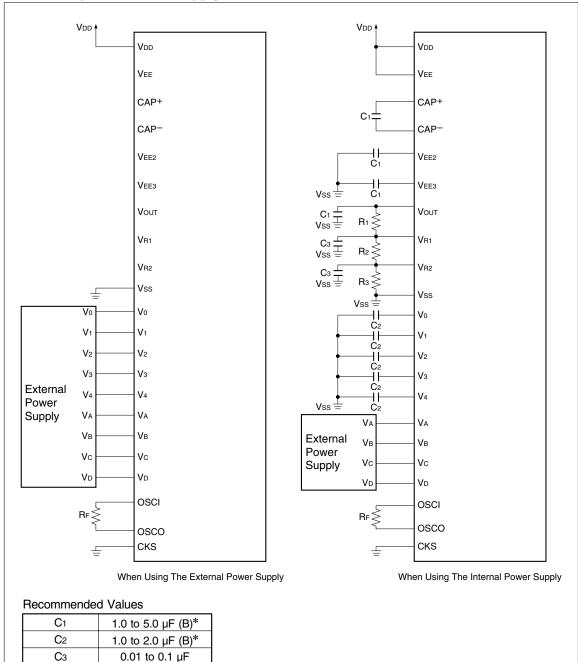

This circuit supplies voltages necessary to drive an LCD panel. This circuit is valid only in the master operation mode. The circuit consists of booster circuit and voltage converter.

Boosted voltage from the booster circuit is fed to the voltage converter which converts this high input voltage into V0, V1, V2, V3 and V4 which are used for graphic display. This internal power supply should not be used to drive a large LCD panel containing many pixels or a large LCD panel that has large capacity consisting of more than one chip. Otherwise, display quality will degrade considerably. Instead, use an external power supply.

This internal power supply is controlled by the power supply circuit ON/OFF command (PON). When the internal power supply is turned off, the booster circuit and voltage converter are also turned off.

When using the external power supply, turn off the internal power supply, disconnect pins CAP+, CAP-, VEE2, VEE3, VOUT, VEE, VR1 and VR2, and keep PMODE pin at VSS. Then, feed external LCD drive voltages to pins Vo, V1, V2, V3, and V4.

This circuit can be changed by the state of PMODE pin.

|        | BOOSTER         | VOLTAGE                                | EXTERNAL                                                                                                                                                          | NOTE                                                                                                                     |

|--------|-----------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| FINODE | CIRCUIT         | CONVERTER                              | VOLTAGE INPUT                                                                                                                                                     | NOTE                                                                                                                     |

| 0      | Disabled        | Disabled                               | V0, V1, V2, V3, V4                                                                                                                                                | 1                                                                                                                        |

| 1      | Disabled        | Disabled                               | V0, V1, V2, V3, V4                                                                                                                                                | 1                                                                                                                        |

| 0      | Enabled         | Enabled                                | -                                                                                                                                                                 |                                                                                                                          |

| 1      | Disabled        | Enabled                                | Vout, Vr1, Vr2                                                                                                                                                    | 2                                                                                                                        |

|        | PMODE<br>0<br>1 | PMODECIRCUIT0Disabled1Disabled0Enabled | CIRCUIT         CONVERTER           0         Disabled         Disabled           1         Disabled         Disabled           0         Enabled         Enabled | PMODECIRCUITCONVERTERVOLTAGE INPUT0DisabledDisabledV0, V1, V2, V3, V41DisabledDisabledV0, V1, V2, V3, V40EnabledEnabled- |

#### NOTES :

Because the booster circuit and voltage converter are not functioning, disconnect pins CAP+, CAP-, VEE2, VEE3, VOUT, VEE, VR1 and VR2.

Apply external LCD drive voltages to corresponding pins.

2. Because the booster circuit is not functioning, disconnect pins CAP+, CAP-, VEE2, VEE3 and VEE. Derive the voltage source to be supplied to the voltage converter from VOUT pin and then output LCD drive voltage to VR1 and VR2 pins. The voltage level at VR1 and VR2 pins must be VR2  $\leq$  VR1  $\leq$  VOUT.

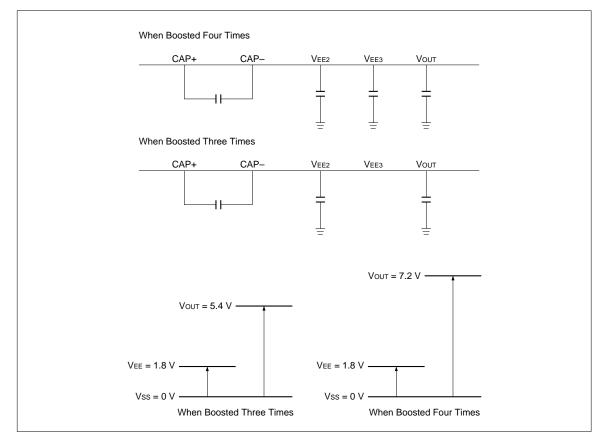

# 2.18. Booster Circuit

Setting BS register, booster circuit multiple can be selected. Placing capacitor C1 across CAP+ and CAP-, across VEE2 and Vss, across VEE3 and Vss and across VOUT and Vss boosts four times.

Placing capacitor C1 across CAP+ and CAP-, across VEE2 and Vss, across Vout and Vss, and setting VEE3 to NC when boosting three times.

Placing C1 across CAP+ and CAP-, across VOUT and Vss, and setting VEE2 and VEE3 to NC when boosting two times.

The boosted voltage is output to VOUT pin.

Since the booster circuit uses the clock derived from the internal oscillation circuit or external clock as the boosting clock, the internal oscillation circuit must be enabled, or if external clock is selected, it must be fed to CK pin.

The output level at the VOUT pin does not exceed the recommended maximum operating voltage (14.0 V) when the voltage is boosted. If this value is exceeded, the operation of the LH155BA is not covered by warranty.

When boosting four times and three times, placement of capacitor is as shown below.

If charge up of LCD drive voltage is not successful, check capacity, voltage dependency and temperature characteristics of external capacitor, and select appropriate device. When charge up is unsuccessful, it is advisable to charge up LCD drive voltage step by step (x 2, x 3, x 4) by inputting software from external microcontroller.

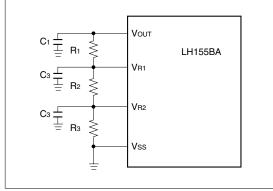

#### 2.19. Voltage Control Circuit

The boosted voltage at the VOUT pin is connected to the VR1 and VR2 pins and then the LCD drive voltages (V0, V1, V2, V3, and V4) are generated via the voltage converter. The input level at the VR1 and VR2 must meet the electric potential condition of VR1  $\geq$  VR2. The internal electronic volume divides the electric potential between the VR1 and VR2 into 16 segments.

Since the VR1 and VR2 pins have high input impedance, the input voltage levels at the VR1 and VR2 are determined by the resistance ratio of R1, R2, and R3. The current flowing between the VOUT and VSS pins is determined by the combined resistance of R1, R2, and R3.

Therefore, R1, R2, and R3 must be selected in accordance with the above current as well as the input voltage levels at the VR1 and VR2.

The boosted voltage at the VOUT pin originates from the voltage supplied at the VEE pin. Thus, the DC path current generated with R1, R2, and R3 connected between the VOUT and VSs pins is supplied as current at the VEE pin. The electric current value, four times larger than the DC path current generated between the VOUT and VSs pins when the voltage is boosted four times, is added as supply current at the VEE pin (three times larger current is added for tripled voltage). Take sufficient care that the input levels at the VR1 and VR2 pins do not fluctuate with external noise (connect capacitor C3).

**Example of Voltage Control Circuit**

#### 2.20. Electronic Volume

The voltage converter incorporates an electronic volume, which allows the LCD drive voltage level V<sub>0</sub> to be controlled with a command and also allows the tone of LCD to be controlled.

If 4-bit data is stored in the register of the electronic volume, one level can be selected among 16 voltage values for the LCD drive voltage Vo. The voltage control range of the electronic volume is determined by the input voltage levels at the VR1 and VR2. This means that the voltage range of (VR1 to VR2) for the graphic display voltage control circuit is the controllable voltage range of the electronic volume. The electric potential relation between the VR1 and VR2 pins must be VR1  $\geq$  VR2. The input voltage levels at the VR1 and VR2 pins must be VR1  $\geq$  VR2. The input voltage levels at the VR1 and VR2 pins must be VR1  $\geq$  VR2. The input voltage levels at the VR1 and VR2 must be selected in accordance with the voltage levels to be obtained with the electronic volume.

### 2.21. LCD Drive Voltage Generation Circuit

The voltage converter contains the voltage generation circuit. The LCD drive voltages other than V<sub>0</sub>, that is, V<sub>1</sub>, V<sub>2</sub>, V<sub>3</sub> and V<sub>4</sub>, are obtained by dividing V<sub>0</sub> through a resistor network. The LCD drive voltage from LH155BA is biased at 1/7 or 1/9 for the graphic display mode and at 1/3 (fixed) for the segment display mode.

When using the internal power supply, connect a stabilizing capacitor C<sub>2</sub> to each of pins V<sub>0</sub> to V<sub>4</sub>.

The capacitance of C<sub>2</sub> should be determined while observing the LCD panel to be used. In this case, connect a capacitor C<sub>3</sub> to stabilize input voltage to  $V_{R1}$  and  $V_{R2}$ . A value of C<sub>3</sub> can be defined selectively.

C3 RF

R1 + R2 + R3

680 kΩ

2.0 to 4.0  $M\Omega$

\* B characteristics must be used with C1 and C2.

# 2.22. Example of Power Supply Circuit Connection

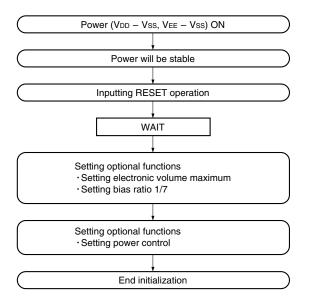

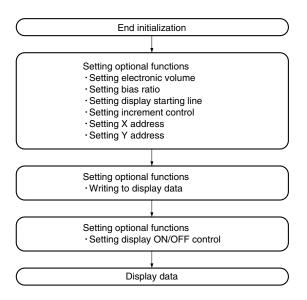

# 2.23. Initialization

The LH155BA is initialized by setting RESB pin to "L". Normally, RESB pin is initialized together with MPU by connecting to the reset pin of MPU.

When power is ON, be sure to reset operation.

| PARAMETER                     | INITIAL STATE              |

|-------------------------------|----------------------------|

| Display RAM                   | Not fixed                  |

| X-address                     | 00н set                    |

| Y-address                     | 00н set                    |

| Display starting line         | Set at the first line (0H) |

| Display ON/OFF                | Display OFF                |

| Display normal/reverse        | Normal                     |

| Display duty                  | 1/64                       |

| n-line alternating            | Every frame unit           |

| Common shift direction        | COM0→COM63                 |

| Increment mode                | Increment OFF              |

| REF mode                      | Normal                     |

| Data SWAP mode                | OFF                        |

| Register in electronic volume | (1, 1, 1, 1)               |

| Power supply                  | OFF                        |

### **3. PRECAUTIONS**

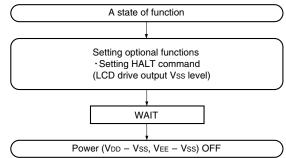

# Precautions when connecting or disconnecting the power supply

This IC may be permanently damaged by a high current which may flow if voltage is supplied to the LCD drive power supply while the logic system power supply is floating. The details are as follows.

- 1) When using an external power supply

- When connecting the power supply After connecting the logic system power supply, make reset operation and then apply external LCD drive voltages to corresponding pins. (Vo, V1, V2, V3, V4 or VOUT, VR1 and VR2)

- When disconnecting the power supply After executing HALT command, disconnect external LCD drive voltages and then disconnect the logic system power supply.

- 2 When using the internal power supply

- When connecting the power supply After connecting the logic system power supply, make reset operation and then execute PON command.

- When disconnecting the power supply After executing HALT command, disconnect the logic system power supply.

It is advisable to connect the serial resistor (50 to 100  $\Omega$ ) or fuse to the LCD drive power Vout or V<sub>0</sub> of the system as a current limiter. Set up a suitable value of the resistor in consideration of the display grade.

# 4. COMMAND FUNCTION

# 4.1. Command Function Table

|                                           | -   | ( | CODI | F   | -   | CODE |    |    |    |            |            |                 |                 |                                                                        |

|-------------------------------------------|-----|---|------|-----|-----|------|----|----|----|------------|------------|-----------------|-----------------|------------------------------------------------------------------------|

| INSTRUCTION                               | CSB |   |      | RDB | RE  | D7   | D6 | D5 | D4 |            | D2         | D1              | Do              | FUNCTION                                                               |

| Display data write                        | 000 | 0 | 0    | 1   | 0   | 0/   | 00 |    |    | D3         |            |                 | 0               | Writes to display RAM.                                                 |

| Display data read                         | 0   | 0 | 1    | 0   | 0   |      |    |    |    | DAT        |            |                 |                 | Reads from display RAM.                                                |

| X address set                             |     |   | _    |     | •   | •    |    |    |    |            |            |                 | _               | Sets X direction address in                                            |

| [Он]                                      | 0   | 1 | 0    | 1   | 0   | 0    | 0  | 0  | 0  |            | x Ad       | dres            | S               | display RAM.                                                           |

| Y address set<br>(Lower) [2H]             | 0   | 1 | 0    | 1   | 0   | 0    | 0  | 1  | 0  | ,<br>,     | Y Ad       | dres            | S               | Sets Y direction address in<br>display RAM.                            |

| Y address set<br>(Upper) [Зн]             | 0   | 1 | 0    | 1   | 0   | 0    | 0  | 1  | 1  | *          |            | Addre           |                 | Sets Y direction address in display RAM.                               |

| Display starting line set<br>(Lower) [4н] | 0   | 1 | 0    | 1   | 0   | 0    | 1  | 0  | 0  | Dis        |            | Star<br>ne      | ting            | Sets line address of RAM making COMo display.                          |

| Display starting line set<br>(Upper) [5н] | 0   | 1 | 0    | 1   | 0   | 0    | 1  | 0  | 1  | *          | *          | Dis<br>Startir  | play<br>Ig Line |                                                                        |

| n-line alternating set<br>(Lower) [6H]    | 0   | 1 | 0    | 1   | 0   | 0    | 1  | 1  | 0  | Alte       | ernat      | ing L           | ine             | Sets the number of alternating reverse line.                           |

| n-line alternating set<br>(Upper) [7н]    | 0   | 1 | 0    | 1   | 0   | 0    | 1  | 1  | 1  | *          | *          | Alterr<br>Li    | nating<br>ne    | Sets the number of alternating reverse line.                           |

| Display control (1) set                   | 0   | 1 | 0    | 1   | 0   | 1    | 0  | 0  | 0  | SHI<br>FT  |            | ALL<br>ON       |                 |                                                                        |

| [8н]                                      | 0   | 1 | U    | 1   | 1   | I    | 0  | 0  | U  | *          | *          | ER              | IR              | ER : Segment's external source<br>IR : Segment source mode             |

| Display control (2) set<br>[9н]           | 0   | 1 | 0    | 1   | 0   | 1    | 0  | 0  | 1  | RE<br>V    | NL<br>IN   | SW<br>AP        | RE<br>F         | 2                                                                      |

| Increment control set<br>[Ан]             | 0   | 1 | 0    | 1   | 0   | 1    | 0  | 1  | 0  | *          | АІМ        | AYI             | AXI             | AIM : Increment mode selection<br>AYI : Y increment, AXI : X increment |

| Power control (1) set<br>[Вн]             | 0   | 1 | 0    | 1   | 0   | 1    | 0  | 1  | 1  | BI<br>AS   | HA<br>LT   | PO<br>N         | AC<br>L         | BIAS : 1/7 or 1/9, HALT : HALT ON<br>PON : Power ON, ACL : reset       |

| Power control (2) set<br>[Dн]             | 0   | 1 | 0    | 1   | 0   | 1    | 1  | 0  | 1  |            |            | OL              |                 | Sets electronic volume for the graphic display.                        |

| Power control (3) set                     | 0   | 1 | 0    | 1   | 0   | 1    | 1  | 1  | 0  | SEG<br>PON |            | EXA             | IC<br>ON        | 3                                                                      |

| [Ен]                                      | 0   | 1 | U    |     | 1   | I    | 1  | 1  | U  |            | ITY<br>DU0 | BS1             | BS0             | DUTY : Selects duty ratio.<br>BS : Selects boosted voltage level.      |

| RE set<br>[Fн]                            | 0   | 1 | 0    | 1   | 0/1 | 1    | 1  | 1  | 1  | *          | *          | *               | RE              | Sets RE flag.                                                          |

| Address set for internal register read    | 0   | 1 | 0    | 1   | 0   | 1    | 1  | 0  | 0  |            |            | ess fo<br>er Re |                 | Sets address of internal register for reading.                         |

| Internal register read                    | 0   | 1 | 1    | 0   | 0   | *    | *  | *  | *  | F          | Read       | Data            | a               | Reads out internal register.                                           |

SHIFT : Common shift direction for the graphic display, SEGON : Segment display ON, ALLON : All graphic display ON, ON/OFF : Graphic display ON/OFF control

② REV : Graphic display normal/reverse, NLIN : nline reverse ON, SWAP : Data for graphic display swap, REF : Segment output for graphic display normal/reverse  ③ SEGPON : Power supply for segment display (Not available now. Set to "0".),

EXA : Clock for segment display external/internal,

ICON : Icon display ON

\* mark means "Don't care".

Parenthesis [] shows address for internal register read.

The LH155BA has a lot of commands, as shown in the list of commands, and each command is explained in detail as follows.

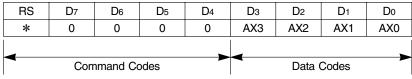

Data codes and command codes are defined as follows and the execution of commands must be made in the chip selection state (CSB = "L").

(For example X address)

\* RS = "0" : RAM data access (Refer to Sections 4.2. and 4.3..)

RS = "1" : Register access (Refer to Sections 4.4. through 4.17..)

The undefined command codes are inhibited.

# 4.2. Data Write to Display RAM

| D7 | D6 | D5   | D4      | Dз      | D2   | D1 | D0 | CSB | RS | WRB | RDB | RE |

|----|----|------|---------|---------|------|----|----|-----|----|-----|-----|----|

|    |    | Disp | lay RAN | 1 Write | Data |    |    | 0   | 0  | 0   | 1   | 0  |

The display RAM data of 8-bit are written in the designated X and Y addresses.

# 4.3. Data Read to Display RAM

| D7 | D6 | D5   | D4      | D3     | D2   | D1 | D0 | CSB | RS | V |

|----|----|------|---------|--------|------|----|----|-----|----|---|

|    |    | Disp | lay RAN | / Read | Data |    |    | 0   | 0  |   |

The 8-bit contents of display RAM designated in X and Y addresses are read out.

Immediately after data are set in X and Y addresses, dummy read is necessary one time.

# 4.4. X Address Register Set

| _ |    |    | •  |    |     |     |     |     |     |    |     |     |    |

|---|----|----|----|----|-----|-----|-----|-----|-----|----|-----|-----|----|

|   | D7 | D6 | D5 | D4 | Dз  | D2  | D1  | Do  | CSB | RS | WRB | RDB | RE |

|   | 0  | 0  | 0  | 0  | AX3 | AX2 | AX1 | AX0 | 0   | 1  | 0   | 1   | 0  |

|   |    |    |    |    |     |     |     |     |     |    |     |     |    |

(At the time of reset : AX3 to AX0 = 0H, read address : 0H)